Macronix’s secure flash memory has been integrated in Nvidia’s next-generation autonomous driving platforms.

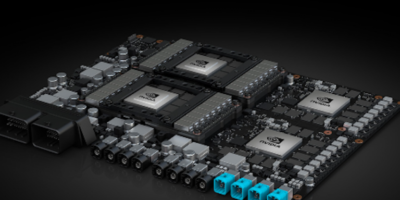

The automotive-grade ArmorFlash memory is being used on the Nvidia Drive AGX Xavier and Drive AGX Pegasus autonomous vehicle computing platforms.

The ArmorFlash memory is secure for data storage in the artificial intelligence (AI)-based Level 2+ advanced driver assistance systems (ADAS) through to Level 5 autonomous driving.

“Our efforts in conjunction with NVIDIA are singularly focused on elevating the security of data in AI-based autonomous driving applications and ultimately, to enhance the safety of drivers,” said Anthony Le, vice president of marketing, Macronix America.

The ArmorFlash memory on the Drive AGX Xavier and Pegasus platforms can provide trusted identification, authentication and encryption features for autonomous driving security requirements.

ArmorFlash offers a combination of mature security technologies, including unique ID, authentication and encryption features. This blend of features enables superior levels of security in a high-density memory device to prevent data from being compromised, claims Macronix.

The ArmorFlash device provides trusted NVM storage of encrypted and integrity-protected assets. The ArmorFlash supports secure communication channel and protocol with the Nvidia Xavier system on a chip (SoC) via cryptographic operations, integrity checks and additional measures against certain security protocol attacks.

The global ADAS market is expected to exceed $67 billion by 2025, fuelled by a compounded annual growth rate of 19 per cent, according to Grand View Research. The research company attributes the growth to increasing government initiatives mandating driver assistance system to lower road accidents and cites expanding adoption of ADAS in small cars as a factor boosting market demand.