Claimed to be the industry’s first high performance sensor hub DSP architecture, SensPro is configurable for parallel processing floating point and integer data types, as well as deep learning training and inferencing.

Ceva has designed it to handle the sensor processing and sensor fusion workloads for contextually-aware devices.

It addresses the need for specialised processors to efficiently handle the proliferation of different types of sensors that are required in smartphones, robotics, automotive, AR/VR headsets, voice assistants, smart home devices and for industrial and medical applications. These camera, radar, lidar, time of flight (ToF) sensors, microphones and inertial measurement units (IMUs) generate data types and bit-rates derived from imaging, sound, RF and motion, which can be used to create a full 3D contextually-aware device, says CEVA.

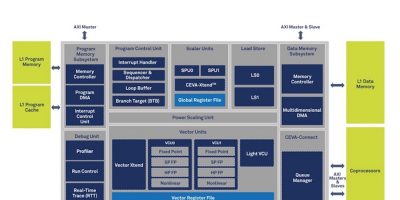

The SensPro architecture is built from the ground up to maximise performance per Watt for multi-sensor processing use cases. It combines high performance single and half precision floating-point maths required for high dynamic range signal processing, point cloud creation and deep neural network (DNN) training. It also has 8-bit and 16-bit parallel processing capacity for voice, imaging, DNN inference processing and simultaneous localisation and mapping (SLAM). SensPro incorporates the Ceva-BX scalar DSP, which offers a seamless migration path from single sensory system designs to multi-sensor, contextual-aware designs.

Dimitrios Damianos, technology and market analyst of the sensing division at Yole Développement (Yole) commented: “The proliferation of sensors in intelligent systems continues to increase, providing more precise modelling of the environment and context. Sensors are becoming smarter, and the goal is not to get more and more data from them, but higher quality of data especially in cases of environment/surround perception. . . . where many sensors . . . must work together to make sense of their surroundings”.

Yohann Tschudi, technology & market analyst, computing and software, at Yole continued: “The challenge is to process and fuse different types of data from different types of sensors. Using a mix of scalar and vector processing, floating and fixed point math coupled with an advanced micro-architecture, SensPro offers system and SoC designers a unified processor architecture to address the needs of any contextually-aware multi-sensor device.”

SensPro uses a configurable eight-way VLIW architecture, allowing it to be easily tuned to address a range of applications. Its micro-architecture combines scalar and vector processing units and incorporates an advanced, deep pipeline enabling operating speeds of 1.6GHz at a 7nm process node.

A Ceva-BX2 scalar processor for control code execution has a 4.3 CoreMark/MHz score. It adopts a wide SIMD scalable processor architecture for parallel processing and is configurable for up to 1024 8×8 MACs, 256 16×16 MACs, dedicated 8×2 binary neural networks support, as well as 64 single precision and 128 half precision floating point MACs. This allows it to deliver 3TOPS for 8×8 networks inferencing, 20TOPS for binary neural networks inferencing, and 400GFLOPS for floating point arithmetic. Additionally, a memory architecture provides a bandwidth of 400Gbyte per second, four-way instruction cache, two-way vector data cache, DMA, and queue and buffer managers for offloading the DSP from data transactions.

Ceva also offers software and development tools, including an LLVM C/C++ compiler, Eclipse based integrated development environment (IDE), OpenVX API, software libraries for OpenCL, Ceva deep neural network (CDNN) graph compiler including the CDNN-Invite API for inclusion of custom AI engines, Ceva-CV imaging functions, Ceva-SLAM software development kit and vision libraries, ClearVox noise reduction, WhisPro speech recognition, MotionEngine sensor fusion, and the SenslinQ software framework.

Initially, SensPro DSPs will be available in three configurations: SP250 (single vector unit with 256 8×8 MACs targeting imaging, vision, and sound centric applications), SP500F (single vector unit with 512 8×8 MACs and 64 single precision floating point MACs targeting SLAM applications) and SP1000 (dual vector units with 1024 8×8 MACs and binary networks support targeting AI applications).

The SensPro architecture and cores will be made available for general licensing from Q3 2020.