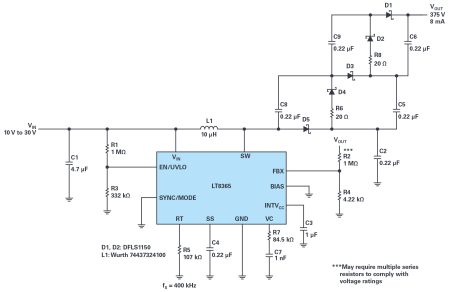

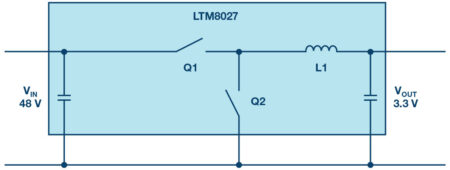

There are different solutions for applications that require conversion from a high input voltage down to a very low output voltage. One interesting example is the conversion from 48V down to 3.3V. Such a specification is not only common in server applications for the information technology market, but in telecommunications as well.Figure 1. Conversion of a voltage from 48V down to 3.3V in one single conversion step.

If a step-down converter (buck) is used for this single conversion step, as shown in Figure 1, the problem of small duty cycles emerges. The duty cycle is the relationship between the on-time (when the main switch is turned on) and the off-time (when the main switch is turned off). A buck converter has a duty cycle, which is defined by the following formula:

![]()

With an input voltage of 48V and an output voltage of 3.3V, the duty cycle is approximately 7%.

This means that at a switching frequency of 1MHz (1000ns per switching period), the Q1 switch is turned on for only 70ns. Then, the Q1 switch is turned off for 930ns and Q2 is turned on. For such a circuit, a switching regulator has to be chosen that allows for a minimum on-time of 70ns or less. If such a component is selected, there is another challenge. Usually the very high power conversion efficiency of a buck regulator is reduced when operating at very short duty cycles. This is because there is only a very short time available to store energy in the inductor. The inductor needs to provide power for a long period during the off-time. This typically leads to very high peak currents in the circuit. To lower these currents, the inductance of L1 needs to be relatively large. This is due to the fact that during the on-time, a large voltage difference is applied across L1 in Figure 1.

In the example, we see about 44.7V across the inductor during the on-time, 48V on the switch-node side, and 3.3V on the output side. The inductor current is calculated by the following formula:

![]()

If there is a high voltage across the inductor, the current rises during a fixed time period and at a fixed inductance. To reduce inductor peak currents, a higher inductance value needs to be selected. However, a higher value inductor adds to increased power losses. Under these voltage conditions, an efficient LTM8027 µModule® regulator from Analog Devices achieves power efficiency of only 80% at 4A output current.

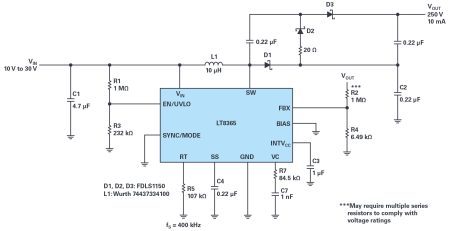

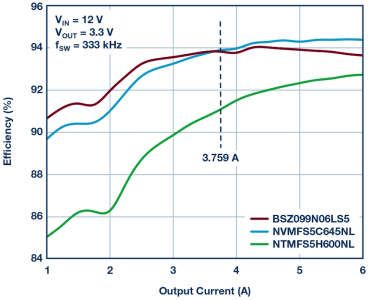

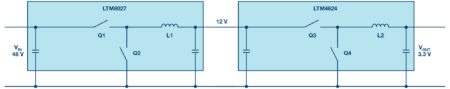

Today, a very common and more efficient circuit solution to increase the power efficiency is the generation of an intermediate voltage. A cascaded setup with two highly efficient step-down (buck) regulators is shown in Figure 2. In the first step, the voltage of 48V is converted to 12V. This voltage is then converted down to 3.3V in a second conversion step. The LTM8027 µModule regulator has a total conversion efficiency of more than 92% when going from 48V down to 12V. The second conversion step from 12V down to 3.3V, performed with a LTM4624, has a conversion efficiency of 90%. This yields a total power conversion efficiency of 83%. This is 3% higher than the direct conversion in Figure 1.

Figure 2. Voltage conversion from 48V down to 3.3V in two steps, including a 12V intermediate voltage.

This can be quite surprising since all the power on the 3.3V output needed to run through two individual switching regulator circuits. The efficiency of the circuit in Figure 1 is lower due to the short duty cycle and the resulting high inductor peak currents.

When comparing single step-down architectures with intermediate bus architectures, there are many more aspects to consider besides power efficiency.

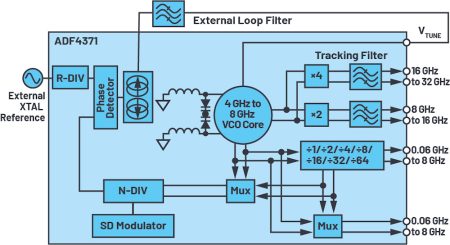

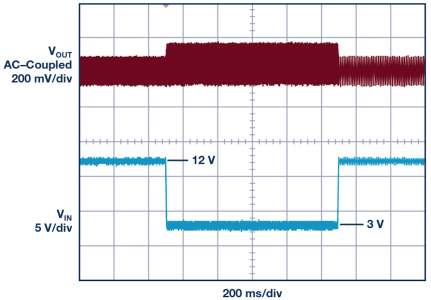

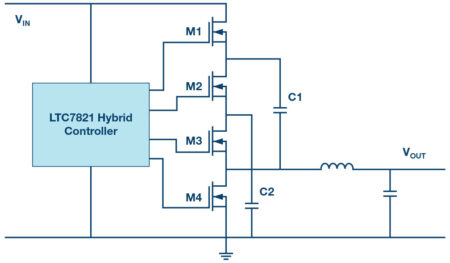

One other solution to this basic problem is the LTC7821, hybrid step-down controller from Analog Devices. It combines charge pump action with a step-down buck regulation. This enables the duty cycle to be 2× VIN/VOUT and, thus, very high step down ratios can be achieved at very high power conversion efficiencies.

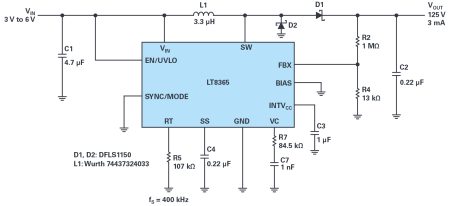

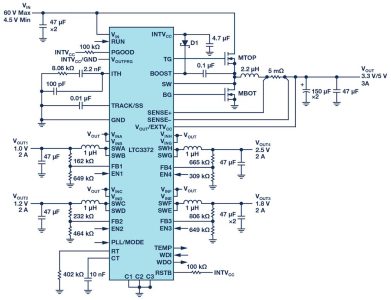

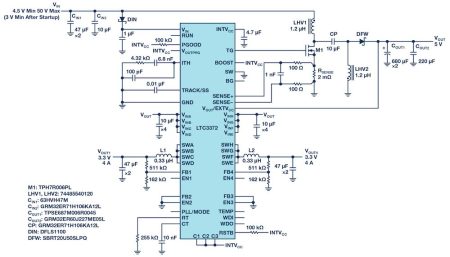

Figure 3 shows the circuit setup of the LTC7821. It is a hybrid step-down synchronous controller. It combines a charge pump to halve the input voltage with a synchronous step-down converter utilising the buck topology. With it, conversion efficiencies of more than 97% for converting 48V to 12V at a 500kHz switching frequency are possible. With other architectures, this high efficiency would only be feasible with much lower switching frequencies. They would require larger inductors.

Figure 3. Circuit design for a hybrid step-down converter.

Four external switching transistors are activated. During operation, the capacitors C1 and C2 generate the charge pump function. The voltage generated in this way is converted into a precisely regulated output voltage with the synchronous buck function. To optimise the EMC characteristics, the charge pump is used with soft switching operations.

The combination of a charge pump and a buck topology offers the following advantages. Due to the optimal combination of charge pump and synchronous switching regulator, the conversion efficiency is very high. The external MOSFETs M2, M3, and M4 only have to withstand low voltages. The circuit is also compact. The coil is smaller and cheaper than in a single-stage converter approach. For this hybrid controller, the duty cycle for switches M1 and M3 is D = 2 × VOUT/VIN. For M2 and M4, the duty cycle is calculated as D = (VIN – 2 × VOUT)/VIN.

For charge pumps, many developers assume a power output limitation of approximately 100mW. The hybrid converter switch with the LTC7821 is designed for output currents of up to 25A. For even higher performance, multiple LTC7821 controllers can be connected in a parallel multiphase configuration with synchronised frequency to share the overall load.

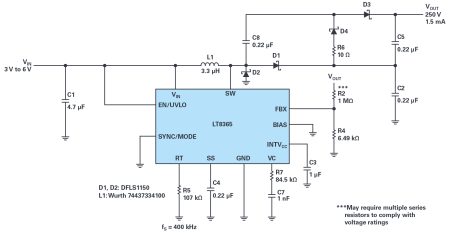

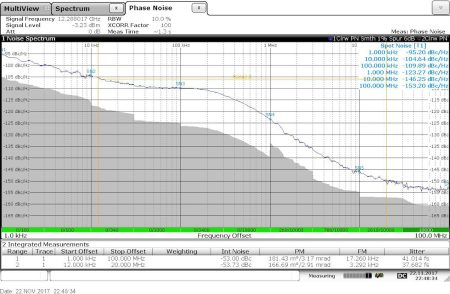

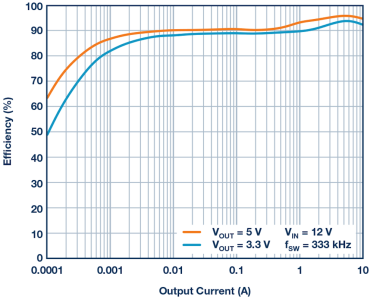

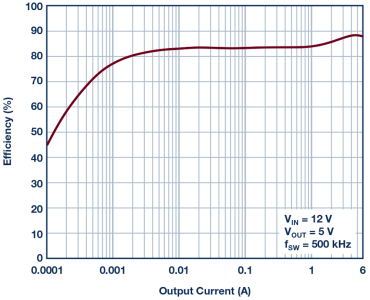

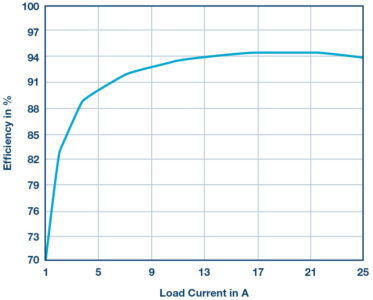

Figure 4. Typical conversion efficiency for converting 48V to 5V at a switching frequency of 500kHz.

Figure 4 shows the typical conversion efficiency for a 48V input voltage and a 5V output voltage at different load currents. At approximately 6 A, a conversion efficiency exceeding 90% is reached. Between 13A and 24A, the efficiency is even higher than 94%.

A hybrid step-down controller supplies very high conversion efficiency in a compact form. It offers an interesting alternative to a discrete two-stage switching regulator design with intermediate bus voltage and to a single-stage converter that is forced to operate at a very low duty cycle. Some designers will prefer a cascaded architecture, others a hybrid architecture. With these two available options, every design should be successful.

Analog Devices: https://www.analog.com

About the Author

Frederik Dostal studied microelectronics at the University of Erlangen-Nuremberg, Germany. Starting work in the power management business in 2001, he has been active in various applications positions including four years in Phoenix, Arizona, working on switch mode power supplies. He joined Analog Devices in 2009 and works as a power management technical expert for Europe. He can be reached at frederik.dostal@analog.com.