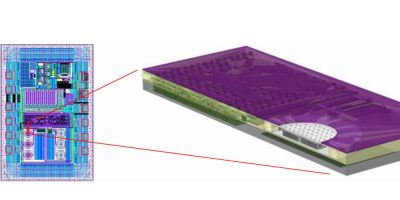

Synopsys combines EDA and IP with Arm’s Total Compute Solutions at Computex Taipei. The AI-enhanced design collaboration tackles mobile chip designs on advanced nodes down to 2nm. At the show, Synopsys announced Synopsys.ai full-stack AI-driven EDA suite, Synopsys Interface and Security IP and Synopsys Silicon Lifecycle Management PVT IP have been optimised for the highest levels of performance and power for Arm’s latest compute platform

These advancements continue the decades of collaboration between the two companies to accelerate customers’ delivery of Arm-based SoCs for smartphones and VR / AR applications.

Shankar Krishnamoorthy, general manager of Synopsys EDA group, commented: “Collaborating with Arm to optimise our EDA and IP solutions enables mutual customers to tackle some of the toughest multi-die system integration challenges from design, IP integration and verification to software development. The addition of the Synopsys.ai EDA suite starts a new phase, where co-operative keystone companies, like Synopsys and Arm, align expertise to help mutual customers turbo-charge the delivery of their Arm-based SoC designs.”

Arm announced its Total Compute Solutions 2023 (TCS23) platform at the show in Taipei. “The new TCS23 platform delivers a suite of segment-specific technology, designed with the system in mind, so that our customers can tap into the compute performance required for the next generation of visual computing experiences,” said Chris Bergey, senior vice president and general manager, client line of business, at Arm.

For TCS23, the Synopsys.ai full-stack AI-driven EDA suite leverages the power of AI from system architecture through manufacturing to optimise power, performance and area (PPA) and enhance time to market, said the company.

The Synopsys Verification family accelerates architecture exploration, software development and verification throughput for Arm SoCs containing Arm Cortex-X4, Cortex-A720 and Cortex-A520 CPUs and Immortalis-G720 and Mali-G720 GPUs.

Early adopters of TCS23 are using Synopsys virtual prototypes with Arm Fast Models, Synopsys hardware-assisted verification and verification IP for the latest Arm AMBA interconnect to deliver SoCs to market faster.

Synopsys Interface and Security IP for PCI Express 6.0 with Integrity and Data Encryption (IDE), CXL 3.0 with IDE, DDR5 with Inline Memory Encryption (IME) and UCIe, are all optimised for performance with Arm-specific features and for pre-silicon interoperability with Arm cores to minimise risk and to accelerate time to market.

The Synopsys Silicon Lifecycle Management Family PVT monitor IP can be integrated into Arm cores to monitor chip health from development to the field to measure and optimise performance.

Synopsys Fusion QuickStart Implementation Kits (QIKs) are tuned to extract maximum entitlement from the latest five, four and 3nm process technologies. They provide the most efficient path to realising optimally scaled compute architectures for the most demanding end-user applications, said the company.

Synopsys QIKs include implementation scripts and reference guides that enable early adopters of the newest Armv9.2 cores to accelerate time to market and achieve their demanding performance per Watt targets. These QIKs are available today by request through the Arm support hub or from Synopsys SolvNet.

Synopsys also incorporates the latest Arm Fast Models for virtual prototypes and delivers verification IP for the latest Arm AMBA interconnect, emulation and prototyping hardware to accelerate hardware-software bring-up and power and performance validation, resulting in shorter time to market.

Synopsys IP for PCI Express 6.0 with IDE, CXL 3.0 with IDE, DDR5 with IME and UCIe are available now.

http://www.synopsys.com