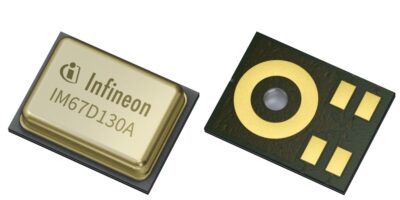

High performance, low noise MEMS microphones are increasingly popular inside and outside of vehicles because of noise quality and hands-free operation. Infineon says it has combined its expertise in the automotive industry, with its MEMS microphones technical know-how to develop the Xensiv IM67D130A. It is claimed to be the first microphone in the market to be qualified for automotive applications.

The Xensiv IM67D130A microphone has a wide operating temperature range of -40C to +105 degrees C for use in harsh automotive environments. The high acoustic overload point (AOP) of 130dB sound pressure level (SPL) allows the microphone to capture distortion-free audio signals in loud environments, enabling it to be effective whether placed inside or outside of the vehicle. The IM67D130A can be used for in-cabin applications such as hands-free systems, emergency calls, in-cabin communication and active noise cancellation (ANC). For exterior applications, it can be used in, for example, siren or road condition detection. Its use allows sound to be a further, complementary sensor for advanced driver assistance systems (ADAS) and predictive maintenance.

The high signal-to-noise ratio (SNR) of 67dB combined with low distortion level are designed for optimum speech quality and speech intelligence for speech recognition applications. The microphones have tight sensitivity matching allowing optimised beamforming algorithms for multi-microphone arrays, added Infineon.

The Xensiv MEMS microphone IM67D130A is qualified for the AEC-Q103-003 standard for automotive applications and available now in PG-LLGA-5-4 package.