Anritsu extends test capabilities for manufacturing wireless communications devices with the Universal Wireless Test Set MT8870A / MT8872A which supports Wi-Fi 7 TRX tests by software options of the WLAN 802.11be TX Measurement MX887034A and WLAN 802.11be Waveforms MV887034A.

The MT8870A / MT8872A has excellent test features for manufacturing inspection of wireless communications equipment and modules, while also supporting all prior Wi-Fi TRX test standards (IEEE 802.11b / g / a / n / ac / ax).

The MX887034A and MV887034A add test features for the latest WLAN IEEE 802.11be Wi-Fi 7 standard to the MT8870A / MT8872A test set. These software options facilitate Wi-Fi 7 TRX testing without changing the manufacturing software and production line configurations in order for customers to optimise the efficiency of their equipment investment.

Offloading mobile data to the WLAN network is important to reduce traffic congestion, said Anritsu. As smartphones, tablets and home appliances, together with automobiles and factory equipment are connecting to the network, network data traffic is likely to continue increasing but the capacity of cellular communication networks, mainly used for mobile phones, is limited.

The latest Wi-Fi 7 WLAN standard attempts to address this, using a wider channel bandwidth and higher order modulation to increase data traffic capacity. A multi-link feature improves the stability of even congested networks. Introduction of Wi-Fi 7 helps implement a more robust communications environment, which is expected to drive further demand for Wi-Fi 7 devices.

Adding MX887034A and MV887034A options is Anritsu’s efficient solution to add Wi-Fi 7 test features to the customer test environment, said the company.

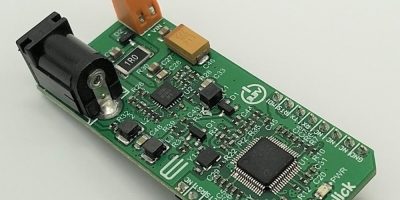

The Universal Wireless Test Set MT8870A / MT8872A series is designed for developing and manufacturing various wireless communication equipment. Installing up to four test units in the main unit supports a seamless frequency band up to 7.3GHz with a 200MHz bandwidth.

Each unit measures test parameters independently in parallel, enabling the MT8870A to quickly and simultaneously evaluate multiple wireless communications devices.