The latest open specification for high performance compute modules will be under review by members of the PICMG, a consortium for the development of open embedded computing specifications.

COM-HPC is the soon-to-be-released PICMG standard for high-performance computer-on-modules (COMs). COM-HPC defines five module sizes to deliver edge server performance for small, rugged data centres. The new specification will complement COM Express, which is expected to play a crucial role in the COM marketplace “for many years”.

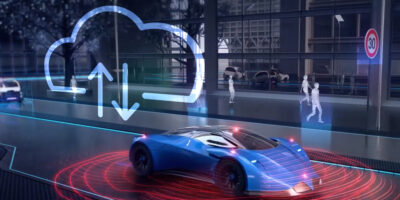

PICMG developed the COM-HPC specification to address emerging requirements in the embedded and edge computing market. These have seen trends, including the substantial data growth and processing requirements of broadband and 5G as well as edge analytic including AI and situational awareness applications come to the fore. IoT devices, sensors, and actuators produce large amounts of data that require pre-processing at the edge for improved data processing efficiency and end to end security. Autonomous vehicles, smart factories, smart retail, medical robotics are among many applications that will benefit from increased edge server and edge client class processors processor modules or COMs available in standard modules that existing standards cannot meet.

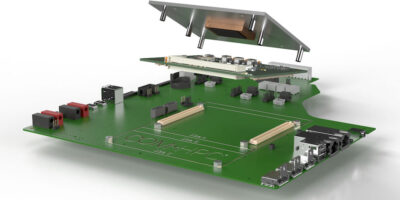

The COM-HPC specification is based on two 400-pin, BGA mount, high-performance connectors and a system management interface. It is not limited to x86 processors and can be used with RISC processors, FPGAs and general purpose GPUs.

The COM-HPC client modules have up to 48 + 1 PCI Express Gen4/5 lanes, up to four USB4 ports and up to four video interfaces and one or two 25Gbit Ethernet interfaces.

Module sizes are 95 x 120mm (Size A), 120 x 120mm (Size B) and 160 x 120mm (Size C).

The COM-HPC server modules are characterised by up to 64 + 1 PCI Express Gen4/5 lanes, one or two USB4 ports, up to four graphic interfaces or are headless. There are up to eight 25Gbit Ethernet interfaces.

Module sizes are 160 x 160mm and 200 x 160mm (Sizes D and E respectively).

Founded in 1994, PICMG is a not-for-profit 501(c) consortium of companies and organisations that collaboratively develop open standards for high performance industrial, Industrial IoT, military and aerospace, telecommunications, test and measurement, medical, and general-purpose embedded computing applications. There are over 130 member companies that specialise in a wide range of technical disciplines, including mechanical and thermal design, single board computer design, high-speed signalling design and analysis, networking expertise, backplane, and packaging design, power management, high availability software and comprehensive system management.

Key standards families developed by PICMG include COM Express, CompactPCI, CompactPCI Serial, AdvancedTCA, MicroTCA, AdvancedMC, COM Express, SHB Express, MicroSAM, and HPM (Hardware Platform Management).