Sfera Labs has announced the first shipments of its new Strato Pi Max flexible and expandable industrial controller based on the Raspberry Pi Compute Module (CM) 4.

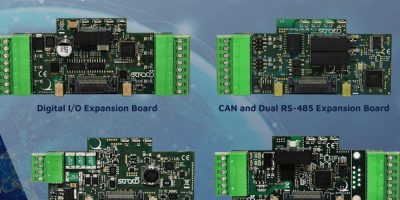

The Strato Pi Max stands out with its modular design, DIN rail-mount, Wi-Fi and BLE wireless connectivity, dual Ethernet ports, dual SD, eMMC, and/or SSD storage options, and two USB ports. It’s a versatile module that can support up to four embedded expansion boards, expanding its capabilities to include serial (RS485/RS232) and CAN bus interfaces, digital I/O, additional wireless connectivity, and support for an uninterruptible power supply (UPS).

Strato Pi Max retains isolated RS-485 port, and USB ports with independent power control and fault detection built into existing members of the Strato Pi family and complies with all relevant industry standards for electrical safety, electromagnetic compatibility (EMC), and sustainability.

Strato Pi Max is offered in two versions: Strato Pi Max XS, which supports up to one expansion board, and Strato Pi Max XL, which supports up to four.

Both models embed pre-assembled CM4 boards with up to 8GB RAM and 32 GB eMMC and can be equipped with a high-performance M.2 PCIe SSD.

Strato Pi Max XL can be ordered in the Lite variant, offering enhanced data reliability with the optional dual SD card.

The Strato Pi Max’s modular architecture is a key feature, allowing it to be tailored to each project’s specific needs. The Strato Pi Max XL can support up to eight interfaces for CAN bus or Modbus, demonstrating its adaptability.

Based on open technology and fully compatible with the toolsets, programming languages, and development frameworks available for Raspberry Pi, the new module will allow designers to implement advanced control systems in industrial, commercial, and residential environments in a shorter timeframe and at a lower cost

https://sferalabs.cc/product/strato-pi-max-xl/

https://sferalabs.cc/product/strato-pi-max-xs/