Automotive OEMs are provided with full-scene emulation via the Radar Scene Emulator introduced by Keysight Technologies. It enables them to lab test complex, real-world scenarios, accelerating the overall speed of test and full vehicle autonomy.

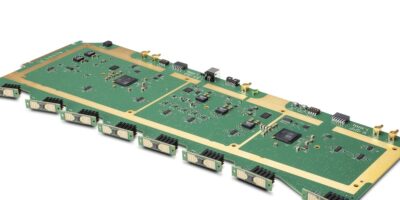

Full-scene emulation in the lab is critical to developing the robust radar sensors and algorithms needed for advanced driver assistance systems (ADAS)/autonomous driving (AD) capabilities. Keysight’s full-scene emulator combines hundreds of miniature radio frequency (RF) front ends into a scalable emulation screen representing up to 512 objects and distances as close as 1.5 meters.

Using full scene rendering that emulates near and far targets across a wide continuous field of view (FOV), Keysight’s Radar Scene Emulator enables customers to rapidly test automotive radar sensors integrated in autonomous driving systems with highly complex multi-target scenes.

Its patented technology shifts emulation away from target simulation for object detection to traffic scene emulation. This approach allows automotive OEMs to see more with a wider, continuous field of view (FOV) and supports both near and far targets. In this way, gaps in a radar’s vision are eliminated, while enabling improved training of algorithms to detect and differentiate multiple objects in dense, complex scenes. As a result, autonomous vehicle decisions can be made based on the complete picture, not just what the test equipment sees, explained Keysight.

Radar sensors can be tested against a limited number of targets, providing an incomplete view of driving scenarios and masking the complexity of the real-world. Keysight’s radar scene emulator allows OEMs to emulate real-world driving scenes in the lab with variations of traffic density, speed, distance and total number of targets. Testing can be completed early for common to corner case scenes, while minimising risk, added the company.

It also provides a deterministic real-world environment for lab testing complex scenes that can presently only be tested on the road. OEMs can “significantly accelerate ADAS/AD algorithm learning by testing scenarios earlier with complex repeatable high-density scenes, with objects stationary or in motion, varying environmental characteristics, while eliminating inefficiencies from manual or robotic automation,” said the company.

There are point clouds (multiple reflections per object), which improve resolution for each object. For example, distinguishing between obstacles on the road which is required for Level 4 and 5 vehicle autonomy as designated by the Society of Automotive Engineers (SAE).

Keysight will demonstrate the Radar Scene Emulator at CES 2022 (5 to 8 January) at Booth 4169, Las Vegas Convention Center, West Hall.

Keysight’s radar scene emulator is part of the company’s Autonomous Drive Emulation (ADE) platform, created through a multi-year collaboration between Keysight, IPG Automotive and Nordsys. The ADE platform exercises ADAS and AD software through the rendering of pre-defined use cases that apply time-synchronised inputs to the actual sensors and sub-systems in a car, such as the global navigation satellite system (GNSS), vehicle to everything (V2X), camera and radar. The open platform, ADE enables automotive OEMs, and their partners, to focus on the development and testing of ADAS/AD systems and algorithms, including sensor fusion and decision-making algorithms. Automotive OEMs can integrate the platform with commercial 3D modelling, hardware-in-the-loop (HIL) systems and existing test and simulation environments.