Tracking technology developed by Anello uses an on-chip waveguide manufacturing process, integrated with a patented silicon photonic IC to enable fibre optic gyro performance with a standard silicon manufacturing process.

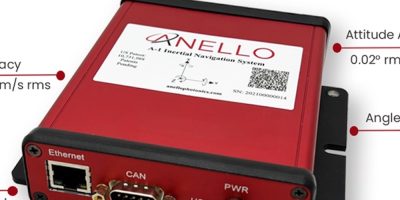

The SIPHOG (Silicon Photonics Optical Gyroscope) is intended for the autonomous navigation market and Anello’s evaluation kit is expected to be used for mapping, surveying, robotics, construction, defence, aerospace and autonomous vehicle applications.

The SIPHOG’s principle of operation is the same as that of the classical interferometric fibre optic gyroscope where the phased modulated light is launched into a waveguide where the light experiences equal but opposite additional phase shifts during rotation. This additional phase shift, due to rotation, is known as the Sagnac effect. The return light from the waveguide is coupled into a photodetector, where the two return beams produce an interference signal that is linearly proportional to the angular rate.

Anello’s low loss on chip waveguide manufacturing process allows the “fibre” in a FOG to be directly replaced by the patented SIPHOG waveguide IC. The IC replaces the discrete optical components (couplers, modulators and detector) found in a FOG. The integrated SIPHOG therefore reduces component costs and dimensional volume compared to an equivalent high performance traditional fibre optic gyro (FOG) implementation.

The manufacturing process is being developed at a large USA-based commercial semiconductor foundry.

Powered by Anello’s optical gyroscope and sensor fusion engine, the evaluation kit can maintain centimetre accuracy in conditions where more expensive ground-truth positioning and localisation systems degrade, said the company. The kit is also accurate in extended full GNSS loss operation. Unlike other positioning and localisation systems, the evaluation kit is more stable over wide temperature ranges and under extreme vibration, said Anello.

The kit has been designed to be easy to use while enabling seamless navigation and positioning in challenging GNSS-denied environments where accuracy is paramount.

Anello reported that it is currently engaged in trials with customers in the automotive, robotics, autonomy, construction, heavy vehicles, defence, aerospace, mapping and surveying markets.

Anello Photonics is based in Santa Clara, California, USA. It has developed an integrated photonic SoC technology for next generation navigation. Its SiPhOG gyroscope is based on its proprietary waveguide process that mimics the properties of optical fibre in an on-chip waveguide.