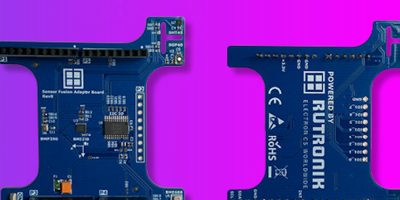

The latest addition to Rutronik System Solutions’ board family is the RAB1 – Sensorfusion. The adapter board offers its own platform that allows machine learning (ML) -based sensor fusion, which forms the basis and the future of artificial intelligence (AI).

It is equipped with sensors from Infineon, Bosch SE and Sensirion. (All sensors are also available in Rutronik’s product portfolio.)

It can be used as a development tool to shorten time to market for a range of applications of sensor fusion, such as air quality measurement or smoke and gas detectors.

Combining and linking different measured values from several sensors, or sensor fusion, is important to gain information, explained Rutronik. The RAB1 Sensorfusion board allows developers to test and select the most suitable components or combination of sensors for an application. The board features the DPS310 barometric air pressure sensor from Infineon, the BMI270 IMU and the BME688 intelligent gas sensor from Bosch Sensortec and the SGP40-D-R4 and the SHT41-AD1B-R2 temperature and humidity sensor from Sensirion. These components can be tested individually or in combination using the board. Rutronik System Solutions provides the software including various application examples. It also has an Arduino interface for use with all other boards, including the Rutronik Basis Board RDK2.

Rutronik Elektronische Bauelemente was founded in 1973 and is an independent family-owned company.

The broad product portfolio includes semiconductors, passive and electromechanical components as well as embedded boards, storage and displays, and wireless products. The company has product areas in the Rutronik Automotive, Rutronik Embedded, Rutronik Power and Rutornik Smart divisions with both specific products and services tailored to the respective applications.

Competent technical support for product development and design-in up to the research area, individual logistics and supply chain management as well as comprehensive services are available.